Bus-holder

A bus-holder (or Bus-keeper) is a weak latch circuit which holds last value on a tri-state bus.

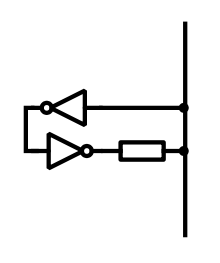

The circuit is basically a delay element with the output connected back to the input through a relatively high impedance. This is usually achieved with two inverters connected back to back. The resistor drives the bus weakly; therefore other circuits can override the value of the bus when they are not in tri-state mode.

Bus-holders are used to prevent CMOS gate inputs from getting floating values when they are connected to tri-stated nets. Otherwise both transistors in the gate could get turned on, thus shorting the power supply and ground, which would destroy the CMOS gate. This is prevented by the bus-holder pulling the input to the last valid logic level (0 or 1) on the net. The circuit is usually placed in parallel with the tri-stated net.

References

- A. P. Godse, D. A. Godse. Digital Logic Design and Application. Technical Publications, 2008. ISBN 978-81-8431-475-5.