Static random-access memory

| Computer memory types |

|---|

| Volatile |

| RAM |

| In development |

| Historical |

|

| Non-volatile |

| ROM |

| NVRAM |

| Early stage NVRAM |

| Mechanical |

| In development |

| Historical |

|

Static random-access memory (static RAM or SRAM) is a type of semiconductor memory that uses bistable latching circuitry (flip-flop) to store each bit. SRAM exhibits data remanence,[1] but it is still volatile in the conventional sense that data is eventually lost when the memory is not powered.

The term static differentiates SRAM from DRAM (dynamic random-access memory) which must be periodically refreshed. SRAM is faster and more expensive than DRAM; it is typically used for CPU cache while DRAM is used for a computer's main memory.

Applications and uses

Characteristics

Advantages:

- Low power consumption

- Simplicity—a refresh circuit is not needed

- Reliability

Disadvantages:

- Price

- Capacity

Clock rate and power

The power consumption of SRAM varies widely depending on how frequently it is accessed; in some instances, it can use as much power as dynamic RAM, when used at high frequencies, and some ICs can consume many watts at full bandwidth. On the other hand, static RAM used at a somewhat slower pace, such as in applications with moderately clocked microprocessors, draws very little power and can have a nearly negligible power consumption when sitting idle – in the region of a few micro-watts. Several techniques have been proposed to manage power consumption of SRAM-based memory structures.[2]

STATIC RAM exists primarily as:

- general purpose products.

- with asynchronous interface, such as the ubiquitous 28-pin 8K × 8 and 32K × 8 chips (often but not always named something along the lines of 6264 and 62C256 respectively), as well as similar products up to 16 Mbit per chip

- with synchronous interface, usually used for caches and other applications requiring burst transfers, up to 18 Mbit (256K × 72) per chip

- integrated on chip

- as RAM or cache memory in micro-controllers (usually from around 32 bytes up to 128 kilobytes)

- as the primary caches in powerful microprocessors, such as the x86 family, and many others (from 8 KB, up to many megabytes)

- to store the registers and parts of the state-machines used in some microprocessors (see register file)

- on application specific ICs, or ASICs (usually in the order of kilobytes)

- in FPGAs and CPLDs

Embedded use

- Many categories of industrial and scientific subsystems, automotive electronics, and similar, contain static RAM.

- Some amount (kilobytes or less) is also embedded in practically all modern appliances, toys, etc. that implement an electronic user interface.

- Several megabytes may be used in complex products such as digital cameras, cell phones, synthesizers, etc.

SRAM in its dual-ported form is sometimes used for realtime digital signal processing circuits.

In computers

SRAM is also used in personal computers, workstations, routers and peripheral equipment: CPU register files, internal CPU caches and external burst mode SRAM caches, hard disk buffers, router buffers, etc. LCD screens and printers also normally employ static RAM to hold the image displayed (or to be printed). Static RAM was used for the main memory of some early personal computers such as the ZX80, TRS-80 Model 100 and Commodore VIC-20.

Hobbyists

Hobbyists, specifically homebuilt processor enthusiasts,[3] often prefer SRAM due to the ease of interfacing. It is much easier to work with than DRAM as there are no refresh cycles and the address and data buses are directly accessible rather than multiplexed. In addition to buses and power connections, SRAM usually requires only three controls: Chip Enable (CE), Write Enable (WE) and Output Enable (OE). In synchronous SRAM, Clock (CLK) is also included.

Types of SRAM

Non-volatile SRAM

Non-volatile SRAMs, or nvSRAMs, have standard SRAM functionality, but they save the data when the power supply is lost, ensuring preservation of critical information. nvSRAMs are used in a wide range of situations—networking, aerospace, and medical, among many others[4] —where the preservation of data is critical and where batteries are impractical.

By transistor type

- Bipolar junction transistor (used in TTL and ECL) – very fast but consumes a lot of power

- MOSFET (used in CMOS) – low power and very common today

By function

- Asynchronous – independent of clock frequency; data in and data out are controlled by address transition

- Synchronous – all timings are initiated by the clock edge(s). Address, data in and other control signals are associated with the clock signals

In 1990s asynchronous SRAM used to be employed for fast access time. Asynchronous SRAM was used as main memory for small cache-less embedded processors used in everything from industrial electronics and measurement systems to hard disks and networking equipment, among many other applications. Nowadays, synchronous SRAM (e.g. DDR SRAM) is rather employed similarly like Synchronous DRAM - DDR SDRAM memory is rather used than asynchronous DRAM (Dynamic random-access memory). Synchronous memory interface is much faster as access time can be significantly reduced by employing pipeline architecture. Furthermore, as DRAM is much cheaper than SRAM, SRAM is often replaced by DRAM, especially in the case when large volume of data is required. SRAM memory is however much faster for random (not block / burst) access. Therefore, SRAM memory is mainly used for CPU cache, small on-chip memory, FIFOs or other small buffers.

By feature

- ZBT (ZBT stands for zero bus turnaround) – the turnaround is the number of clock cycles it takes to change access to the SRAM from write to read and vice versa. The turnaround for ZBT SRAMs or the latency between read and write cycle is zero.

- syncBurst (syncBurst SRAM or synchronous-burst SRAM) – features synchronous burst write access to the SRAM to increase write operation to the SRAM

- DDR SRAM – Synchronous, single read/write port, double data rate I/O

- Quad Data Rate SRAM – Synchronous, separate read and write ports, quadruple data rate I/O

By flip-flop type

- Binary SRAM

- Ternary SRAM

Design

.svg.png)

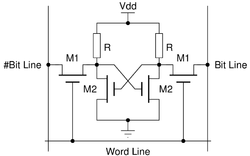

A typical SRAM cell is made up of six MOSFETs. Each bit in an SRAM is stored on four transistors (M1, M2, M3, M4) that form two cross-coupled inverters. This storage cell has two stable states which are used to denote 0 and 1. Two additional access transistors serve to control the access to a storage cell during read and write operations. In addition to such six-transistor (6T) SRAM, other kinds of SRAM chips use 4, 8, 10 (4T, 8T, 10T SRAM), or more transistors per bit.[5][6][7] Four-transistor SRAM is quite common in stand-alone SRAM devices (as opposed to SRAM used for CPU caches), implemented in special processes with an extra layer of polysilicon, allowing for very high-resistance pull-up resistors.[8] The principal drawback of using 4T SRAM is increased static power due to the constant current flow through one of the pull-down transistors.

This is sometimes used to implement more than one (read and/or write) port, which may be useful in certain types of video memory and register files implemented with multi-ported SRAM circuitry.

Generally, the fewer transistors needed per cell, the smaller each cell can be. Since the cost of processing a silicon wafer is relatively fixed, using smaller cells and so packing more bits on one wafer reduces the cost per bit of memory.

Memory cells that use fewer than four transistors are possible – but, such 3T[9][10] or 1T cells are DRAM, not SRAM (even the so-called 1T-SRAM).

Access to the cell is enabled by the word line (WL in figure) which controls the two access transistors M5 and M6 which, in turn, control whether the cell should be connected to the bit lines: BL and BL. They are used to transfer data for both read and write operations. Although it is not strictly necessary to have two bit lines, both the signal and its inverse are typically provided in order to improve noise margins.

During read accesses, the bit lines are actively driven high and low by the inverters in the SRAM cell. This improves SRAM bandwidth compared to DRAMs – in a DRAM, the bit line is connected to storage capacitors and charge sharing causes the bitline to swing upwards or downwards. The symmetric structure of SRAMs also allows for differential signaling, which makes small voltage swings more easily detectable. Another difference with DRAM that contributes to making SRAM faster is that commercial chips accept all address bits at a time. By comparison, commodity DRAMs have the address multiplexed in two halves, i.e. higher bits followed by lower bits, over the same package pins in order to keep their size and cost down.

The size of an SRAM with m address lines and n data lines is 2m words, or 2m × n bits. The most common word size is 8 bits, meaning that a single byte can be read or written to each of 2m different words within the SRAM chip. Several common SRAM chips have 11 address lines (thus a capacity of 2m = 2,048 = 2k words) and an 8-bit word, so they are referred to as "2k × 8 SRAM".

SRAM operation

An SRAM cell has three different states: standby (the circuit is idle), reading (the data has been requested) or writing (updating the contents). SRAM operating in read mode and write modes should have "readability" and "write stability", respectively. The three different states work as follows:

- Standby

- If the word line is not asserted, the access transistors M5 and M6 disconnect the cell from the bit lines. The two cross-coupled inverters formed by M1 – M4 will continue to reinforce each other as long as they are connected to the supply.

- Reading

- In theory, reading only requires asserting the word line WL and reading the SRAM cell state by a single access transistor and bit line, e.g. M6, BL. Nevertheless, bit lines are relatively long and have large parasitic capacitance. To speed up reading, a more complex process is used in practice: The read cycle is started by precharging both bit lines BL and BL, i.e., driving the bit lines to a threshold voltage (midrange voltage between logical 1 and 0) by an external module (not shown in the figures). Then asserting the word line WL enables both the access transistors M5 and M6, which causes the bit line BL voltage to either slightly drop (bottom NMOS transistor M3 is ON and top PMOS transistor M4 is off) or rise (top PMOS transistor M4 is on). It should be noted that if BL voltage rises, the BL voltage drops, and vice versa. Then the BL and BL lines will have a small voltage difference between them. A sense amplifier will sense which line has the higher voltage and thus determine whether there was 1 or 0 stored. The higher the sensitivity of the sense amplifier, the faster the read operation.

- Writing

- The write cycle begins by applying the value to be written to the bit lines. If we wish to write a 0, we would apply a 0 to the bit lines, i.e. setting BL to 1 and BL to 0. This is similar to applying a reset pulse to an SR-latch, which causes the flip flop to change state. A 1 is written by inverting the values of the bit lines. WL is then asserted and the value that is to be stored is latched in. This works because the bit line input-drivers are designed to be much stronger than the relatively weak transistors in the cell itself so they can easily override the previous state of the cross-coupled inverters. In practice, access NMOS transistors M5 and M6 have to be stronger than either bottom NMOS (M1, M3) or top PMOS (M2, M4) transistors. This is easily obtained as PMOS transistors are much weaker than NMOS when same sized. Consequently when one transistor pair (e.g. M3 and M4) is only slightly overriden by the write process, the opposite transistors pair (M1 and M2) gate voltage is also changed. This means that the M1 and M2 transistors can be easier overriden, and so on. Thus, cross-coupled inverters magnify the writing process.

Bus behavior

RAM with an access time of 70 ns will output valid data within 70 ns from the time that the address lines are valid. But the data will remain for a hold time as well (5–10 ns). Rise and fall times also influence valid timeslots with approximately 5 ns. By reading the lower part of an address range, bits in sequence (page cycle) one can read with significantly shorter access time (30 ns).[11]

See also

- DRAM, which also includes PSRAM (pseudo-static RAM)

- Flash memory

- Transistor

- Miniature Card, a discontinued SRAM memory card standard

References

- ↑ Sergei Skorobogatov (June 2002). "Low temperature data remanence in static RAM". University of Cambridge, Computer Laboratory. Retrieved 2008-02-27.

- ↑ "A Survey of Architectural Techniques For Improving Cache Power Efficiency", S. Mittal, SUSCOM, 4(1), 33-43, 2014

- ↑ "Homemade CPU".

- ↑ Computer organization. (4th ed.). [S.l.]: McGraw-Hill. ISBN 0-07-114323-8.

- ↑ A 160 mV Robust Schmitt Trigger Based Subthreshold SRAM

- ↑ United States Patent 6975532: Quasi-static random access memory

- ↑

- ↑ Preston, Ronald P. (2001). "14: Register Files and Caches" (PDF). The Design of High Performance Microprocessor Circuits. IEEE Press. p. 290.

- ↑ United States Patent 6975531: 6F2 3-transistor DRAM gain cell

- ↑ 3T-iRAM(r) Technology

- ↑ "Tentative Toshiba mos digital integrated circuit silicon gate cmos 4,194,304-word by 16-bit cmos pseudo static RAM" (PDF). 070731 toshiba.com